# Multi-line buffer based pipeline architecture with Junction Connectivity and Inflection point selection for High Frame Rate and Ultra-Low Delay Contour-Based Corner Detection

查欣婧 池永研究室 修士課程修了

## Background

- Application

- Workpiece positioning

- Quality inspection

- Motion tracking

- **.**..

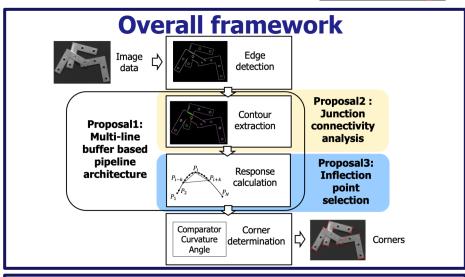

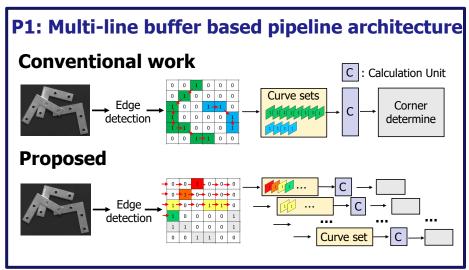

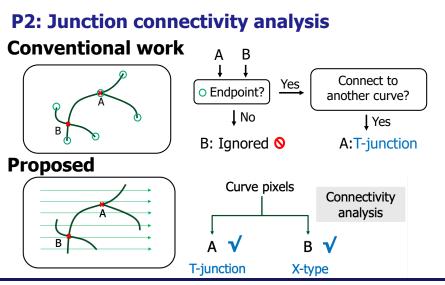

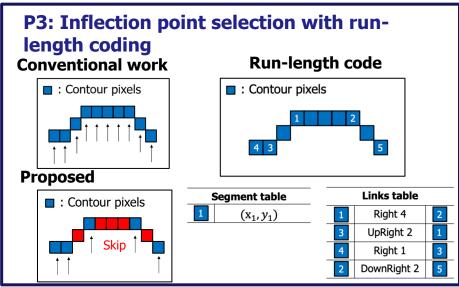

### Proposed method

- Target

- High frame rate and ultra-low delay (1 msec/ frame) contour-based corner detection on FPGA

- Challenges

- High accuracy and discrimination requirement

- Ultra-low delay processing

- **.**..

### Experiments Result

|               | Average Repeatability | Localization Error |

|---------------|-----------------------|--------------------|

| Harris        | 0.5322398             | 0.7323982          |

| CTAR          | 0.5832133             | 0.4373855          |

| CTAR+P1       | 0.5714989             | 0.4284971          |

| CTAR+P1+P2+P3 | 0.5714989             | 0.4284971          |

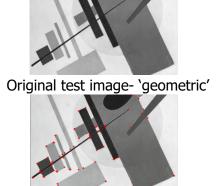

Results of conventional CTAR

Results of CTAR + Proposal

#### Conclusion

■ Hardware-oriented contour-based corner detection algorithm for high frame rate and ultra-low delay system